二进制乘法器

×+1100110111100000010101110001000101111010100

M位(X=i=0∑M−1Xi2i)×N位(Y=j=0∑N−1Yj2j)

结果(将 Z 展开为 X 和 Y 的乘积形式):

Z=X×Y=k=0∑M+N−1Zk2k=(i=0∑M−1Xi2i)(j=0∑N−1Yj2j)

=i=0∑M−1(j=0∑N−1XiYj2i+j)=i=0∑M−1j=0∑N−1(XiYj)⋅2i+j

我们可以构建一个M行N列的位积矩阵(这个M行N列的矩阵中的每一个元素XiYj都代表一次AND操作):

位积矩阵=XM−1YN−1XM−2YN−1⋮X0YN−1XM−1YN−2XM−2YN−2⋮X0YN−2⋯⋯⋱⋯XM−1Y0XM−2Y0⋮X0Y0

最终乘积Z是这个矩阵中所有元素乘以其对应的二进制权重后的总和。矩阵中位于第i行、第j列的元素XiYj的权重是2i+j。

由于符号位有负的权重,所以 X 和Y 可以解构为:

X=-x_{m-1}2^{m-1}+\sum_{i=0}^{m-2} x_{i}2^{i}

$$ $$

Y=-y_{n-1}2^{n-1}+\sum_{i=0}^{n-2} y_{i}2^{i}

由此,乘积结果可表示为:

XY=xm−1yn−12m+n−2+i=0∑i=n−2j=0∑j=m−2xjyi2m+n−4−(xm−1i=0∑n−2yi2m+i−1+yn−1i=0∑m−2xi2n+i−1)

难点在于出现了减法。在数字集成电路设计中,我们希望只使用加法器阵列。因此,必须利用补码的性质将“减法”转换为“加法”。

+x3y311S6x2y3x3y2S5x2y2x1y3x3y1S4x3y3x2y1x1y2x0y3x3y0S3x2y2x2y0x1y1x0y211S2x1y1x1y0x0y111S1x0y0x0y01111S0

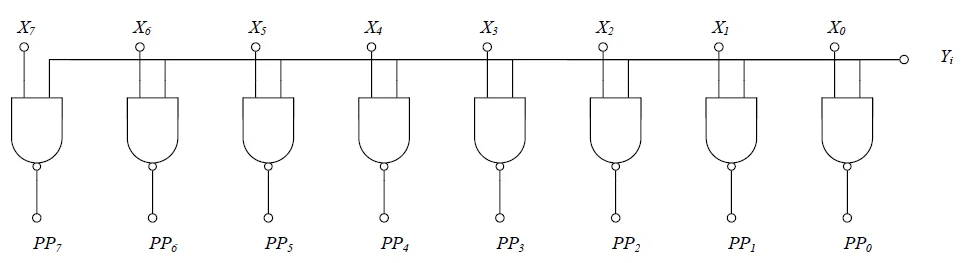

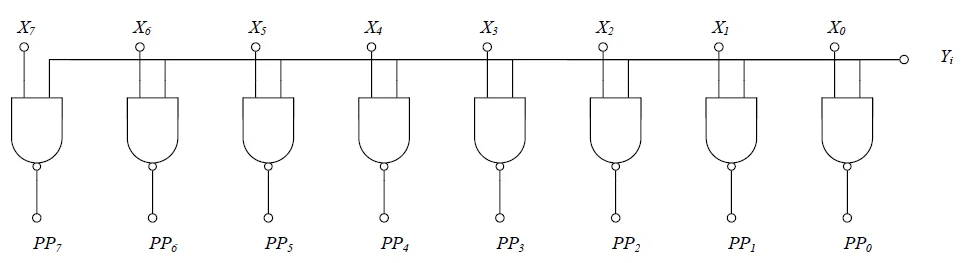

部分积的产生

部分积产生电路

这里的与门使用的是 NAND ,由于加法器的反相特性,虽然NAND门的输出是AND门输出的反码,但后续的电路(如加法器)通常可以设计为接受反相输入,或者利用加法器本身的逻辑特性来抵消这个反相。

如果乘数中某一位是0,该行部分积全为0,对结果无贡献。但我们无法控制输入数据中0的数量。

编码目标:通过对乘数进行编码,将连续的“1”序列转换为更稀疏的形式,从而减少实际需要运算的非零项数目。

每次乘数中取 k 位(例如2位),即取: 00 、 01 、 10 、 11

如果经典 Booth 编码每次取2位(基4 Booth),根据原本的二进制权重是 1 和 2,组合起来可能出现 1+2=3 的情况。

在硬件中,计算 3×X 需要将 X 左移一位(得到 2X)再通过加法器加上 X(得到 3X)。但是这个加法操作会带来延时。

在常规二进制中,权重只能是正的(20,21)。但是改进的 Booth 编码将其扩展为带符号的数字集 如 {−2,−1,0,1,2}。通过引入负系数,将 3 重新编码。在更高基数下,可以将 3 表示为 4−1。

其中:

-

4X 是左移两位(无延时)。

-

−1X 是取反加一(简单逻辑)。

2i+k−1+2i+k−2+⋯+2i=2i(2k−1)=2i+k−2i

正常的逻辑是凑低位的相加得到任意数字(但是可能要加很多次,延时变长),但是现在思路换成:==无论连续的“1”有多长,我们都可以用一次高位加法和一次低位减法来替代中间所有的加法运算==。

部分积的累加

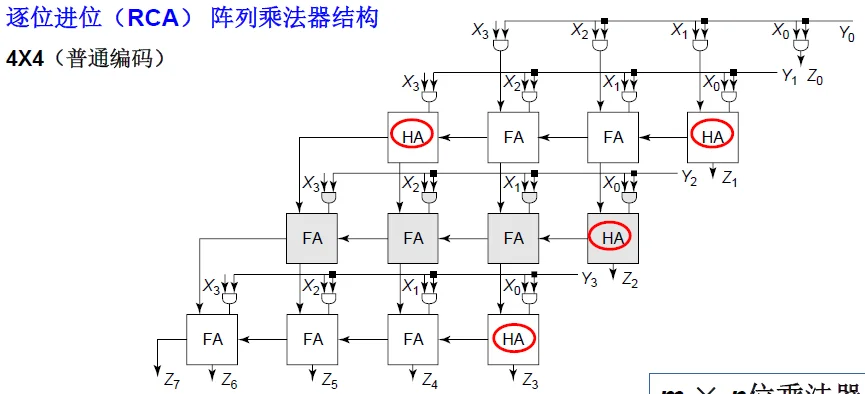

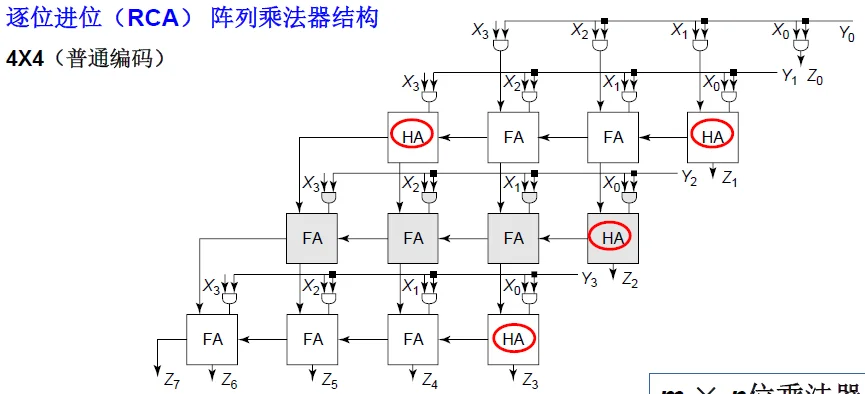

逐位进位阵列乘法器结构

第一行:

最终相加

高性能乘法器架构

其他数据通路设计

-

逻辑移位:

- 最基础的移位。无论左移还是右移,空出的位统一补0。主要用于无符号数的处理或单纯的位操作。

-

算术移位:

-

循环移位:

- 数据像在圆环中移动,移出的位会被填补到另一端空出的位置,不会丢失数据。

什么是TPU